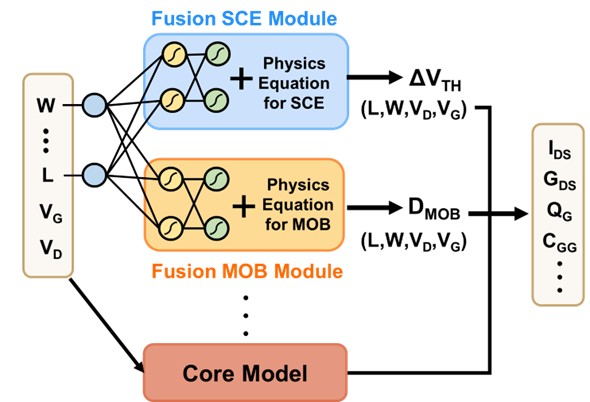

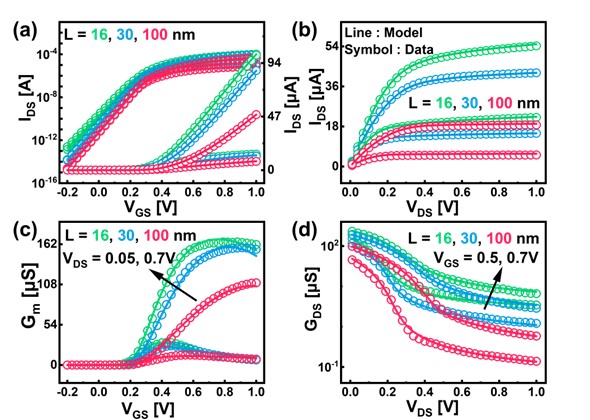

[1] B. Peng, F. Zhang, W. Dai, H. Wu, G. Cheng, R. Wang, M. Chan, L. Zhang, “PHIMO-NN: Compact Modeling by Fusing Device Physics and Neural Networks for One-shot Parameterization,” to appear in IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, DOI: 10.1109/TCAD.2025.3590659

[2] S. Chen, B. Peng, Y. Jiao, Y. Li, L. Zhang, Z. Sun, Y. Xue, Z. Ji, R. Wang, R. Huang, “Self-heating effects of vertical gate-all-around transistors: analysis and modeling,” IEEE Trans. Electron Devices, vol. 71, no. 11, pp. 6478 - 6485, Nov. 2024

[3] B. Peng, Y. Jiao, H. Zhong, Z. Rong, Z. Wang, Y. Xiao, W. Wong, L. Zhang, R. Wang, R. Huang, “Compact modeling of quantum confinements in nanoscale gate-all-around MOSFETs,” Fundamental Research, vol. 4, issue 5, pp. 1306-1313, Sept. 2024

[4] B. Peng, S. Chen, Y. Li, L. Zhang, H. Wu, M. Li, R. Wang, R. Huang, “Modeling the parasitic resistances and capacitances of advanced vertical gate-all-around transistors,” IEEE Trans. Electron Devices, vol. 71, no. 1, pp. 461-467, Jan. 2024.